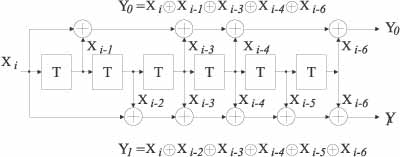

Двоичное пакетное сверточное кодирование PBCC. Скорости передачи 5,5 и 11 Мбит/сКроме комплементарных CCK-последовательностей, в стандарте IEEE 802.11g для скоростей 5,5 и 11 Мбит/с опционально предусмотрено использование технологии двоичного пакетного сверточного кодирования PBCC. В основе метода PBCC лежит так называемое сверточное кодирование со скоростью 1/2. Сверточное кодирование подразумевает, что входной последовательности битов {Xi} ставится в соответствие по определенному алгоритму выходная последовательность битов {Yi}, причем значение каждого бита выходной последовательности зависит от значения нескольких битов входной последовательности, то есть для расчета одного бита выходной последовательности учитывается некоторая предыстория входной последовательности. Для того чтобы значение выходного бита зависело от значений нескольких битов входной последовательности, в сверточном кодере применяются запоминающие ячейки и логические элементы XOR. Кроме того, любой сверточный кодер подразумевает определенную степень избыточности, что повышает помехоустойчивость закодированной информации. В протоколе 802.11g используются сверточные кодеры, состоящие из шести запоминающих ячеек

Поэтому всего существует семь различных состояний входного сигнала: текущее и шесть значений, хранящихся в запоминающих ячейках. Такие кодеры называются сверточными кодерами на семь состояний (K = 7). Кроме того, каждому входному биту X0 ставятся в соответствие два выходных бита — Y0 и Y1. Если скорость входной последовательности составляет k бит/с, то скорость выходной последовательности — k дибит/с или 2k бит/с. При этом говорят, что скорость кодирования равна 1/2. Значение каждого формируемого дибита {Y0, Y1} зависит не только от входящего информационного бита X0, но и от шести предыдущих битов, значения которых хранятся в двух запоминающих ячейках. Главным достоинством сверточных кодеров является помехоустойчивость формируемой ими последовательности. Дело в том, что при избыточности кодирования (вспомним, что каждому информационному биту ставится в соответствие дибит) даже в случае возникновения ошибок приема (к примеру, вместо дибита 11 ошибочно принят дибит 10) исходная последовательность битов может быть безошибочно восстановлена. Для этого на стороне приемника применяется декодер Витерби. Дибит {Y0, Y1}, формируемый в сверточном кодере, используется в дальнейшем в качестве передаваемого символа, но предварительно он подвергается фазовой модуляции

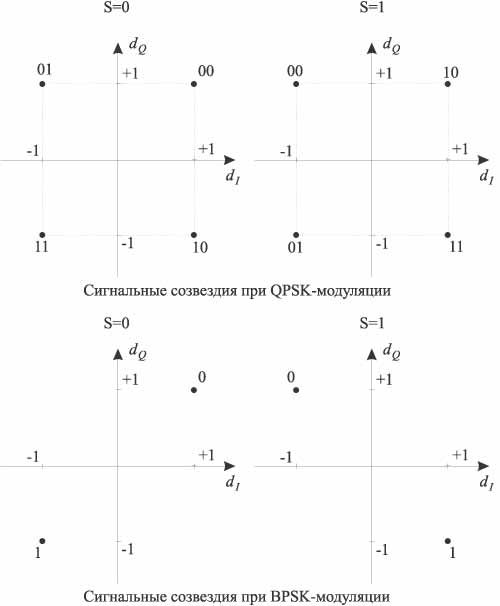

Если скорость передачи составляет 11 Мбит/с, то применяется квадратичная фазовая модуляция QPSK. В данном случае каждому из четырех возможных состояний дибита соответствует одна из четырех возможных фаз. При этом в каждом символе кодируется по одному входному биту, а скорость передачи битов соответствует скорости передачи символов. Если же скорость передачи составляет 5,5 Мбит/с, то используется двоичная фазовая модуляция BPSK. Каждый бит Y0 или Y1, формируемый сверточным кодером, последовательно подвергается фазовой модуляции. Поскольку каждому входному биту в данном случае соответствуют два выходных символа, скорость передачи битов равна половине скорости передачи символов. Поэтому для скорости и 5,5 и 11 Мбит/с символьная скорость составляет 11Ѕ106 символов в секунду. При применении технологии двоичного пакетного сверточного кодирования PBCC необходимо, чтобы ширина спектра передаваемого сигнала оставалась такой же, как и в случае CCK-последовательностей или кодов Баркера, то есть была бы равна 22 МГц. В отличие от технологии DSSS, в этом случае используется не технология уширения спектра, а шумоподобные последовательности, однако и здесь предусмотрено уширение спектра до стандартных 22 МГц. Для этого применяют вариации возможных сигнальных созвездий QPSK и BPSK. Напомним, что сигнальные созвездия представляют собой геометрическое отображение возможных выходных состояний сигнала. Для QPSK-модуляции имеются четыре дискретных состояния сигнала: 00, 01, 10 и 11. Каждому из этих дибитов соответствует одна из четырех возможных фаз несущего сигнала. Понятно, что расположение точек на сигнальном созвездии может быть различным. Именно этот принцип реализован в методе PBCC для уширения спектра выходного сигнала: используются по два сигнальных созвездия QPSK и BPSK

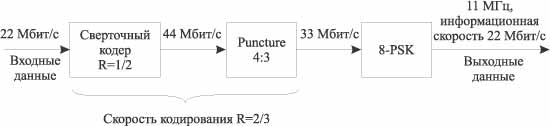

Выбор между конкретным типом применяемого созвездия задается управляющим сигналом S, принимающим значение 0 или 1. Этот сигнал задается псевдослучайной последовательностью с периодом повторения 256 бит, которая формируется из 16-битной базовой последовательности 0011001110001011. Для того чтобы из данной базовой 16-битной последовательности получить 256-битную, используют циклический сдвиг трех первых символов одновременно. Так получают еще пятнадцать 16-битовых последовательностей, что в сумме дает одну 256-битную. Как уже отмечалось, рассмотренный метод PBCC-кодирования опционально используется как в протоколе 802.11g, так и в протоколе 802.11b/b+ на скоростях 5,5 и 11 Мбит/с. Пунктурное кодирование. Скорости передачи 22 и 33 Мбит/сОпционально в протоколе 802.11g технология двоичного пакетного сверточного кодирования PBCC может применяться при скоростях передачи 22 и 33 Мбит/с. Отметим, что скорость 22 Мбит/с при использовании технологии PBCC предусмотрена и в стандарте 802.11b+. При скорости 22 Мбит/с, по сравнению с уже рассмотренной нами схемой PBCC, имеются два отличия. Прежде всего, применяется не квадратичная, а 8-позиционная фазовая модуляция 8-PSK, то есть фаза сигнала может принимать восемь различных значений. Это позволяет в одном символе кодировать уже не два, а три бита и, следовательно, увеличить информационную скорость передачи. Кроме сверточного кодера в схему добавлен пунктурный кодер (Puncture). Смысл такого решения достаточно прост: избыточность сверточного кодера равная 2 (на каждый входной бит приходятся два выходных) достаточна высока и при определенных условиях помеховой обстановки является излишней, поэтому можно уменьшить избыточность, чтобы, к примеру, каждым двум входным битам соответствовали три выходных. Для этого можно, конечно, разработать соответствующий сверточный кодер, но лучше добавить в схему блок, который будет просто уничтожать лишние биты. Допустим, что пунктурный кодер удаляет один бит из каждых четырех входных битов. Тогда каждым четырем входящим битам будут соответствовать три выходящих. Скорость такого кодера составляет 4:3.

Если же такой кодер используется в паре со сверточным кодером со скоростью 1/2, то общая скорость кодирования составляет уже 2/3, то есть каждым двум входным битам будут соответствовать три выходных. Поняв принцип работы пунктурного кодера, вернемся к рассмотрению кодирования PBCC на скорости 22 Мбит/с в протоколе 802.11g. В сверточный кодер (K = 7, R = 1/2) данные поступают со скоростью 22 Мбит/с. После добавления избыточности в сверточном кодере биты со скоростью потока 44 Мбит/с поступают в пунктурный кодер 4:3, в котором избыточность уменьшается так, чтобы на каждые четыре входных бита приходились три выходных. Следовательно, после пунктурного кодера скорость потока составит уже 33 Мбит/с (не информационная скорость, а общая скорость с учетом добавленных избыточных битов). Полученная в результате последовательность направляется в фазовый модулятор 8-PSK, где каждые три бита упаковываются в один символ. При этом скорость передачи составит 11Ѕ106 символов в секунду, а информационная скорость — 22 Мбит/с

Аналогичная технология кодирования предусматривается протоколом 802.11g и на скорости 33 Мбит/с, но для повышения скорости используются увеличение входной скорости данных (до 33 Мбит/с) и еще большее уменьшение избыточности (пунктурный кодер 2:1). В результате при символьной скорости 11Ѕ106 символов в секунду информационная скорость составляет 33 Мбит/с. |